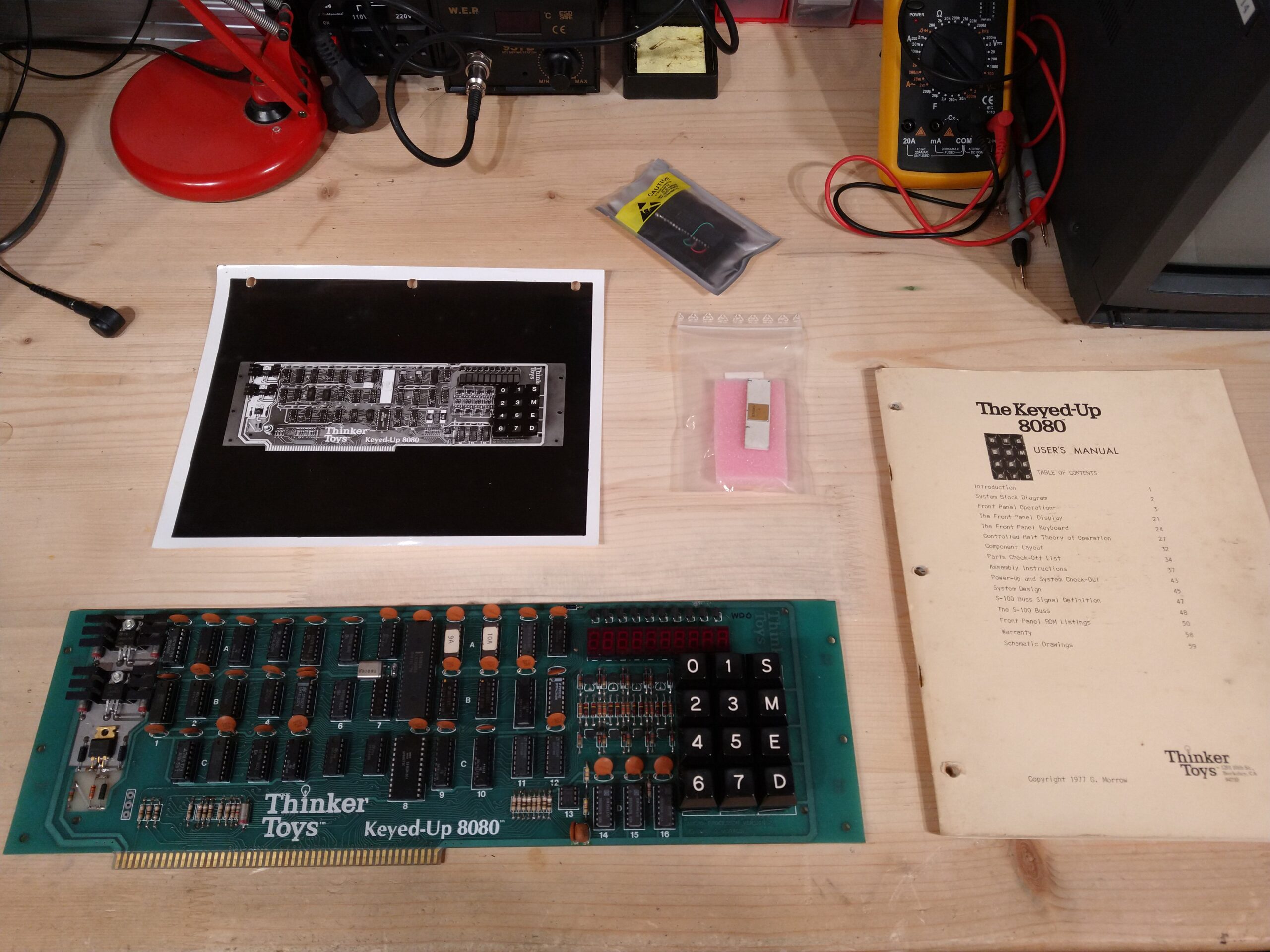

Esta placa madre, basada en la arquitectura de bus S-100 y dotada de un procesador 8080, fue desarrollada por George Morrow a finales de los años 70 y cuenta, entre otras particularidades, con un panel frontal con un teclado de entrada de datos y un display, ambos en formato octal.

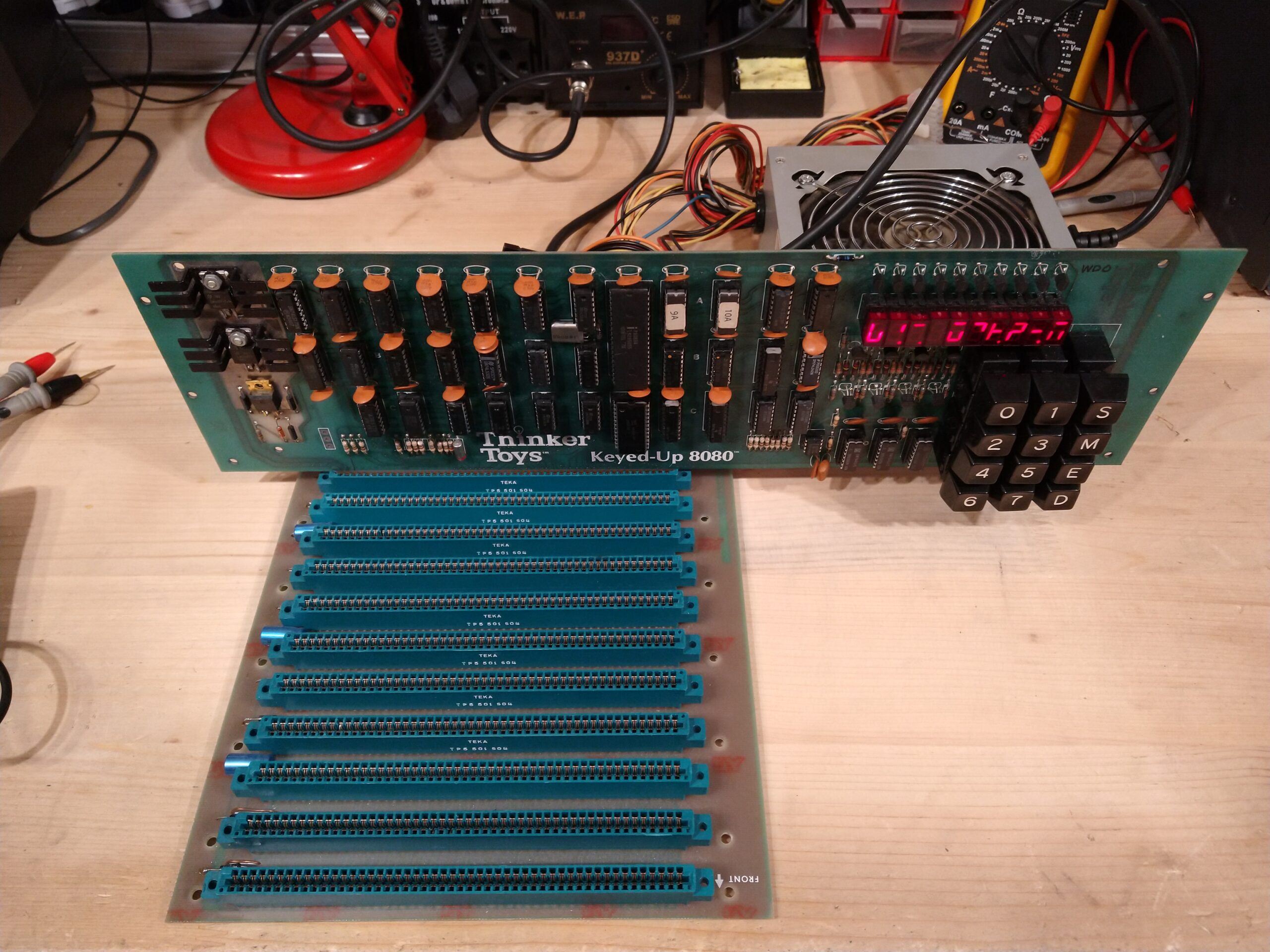

La tarjeta fue probada en un backplane S-100 de Vector Graphics, modificado para suministro de voltajes desde una fuente de alimentación ATX, modificando al mismo tiempo y de forma temporal los reguladores de voltaje de la placa para adaptarse a estos valores de tensión.

Se observa durante el encendido que el display muestra basura y que la tarjeta se encuentra en un estado no funcional.

Se procede a la revisión de los circuitos que intervienen en el arranque del procesador, y se utiliza un generador NOP (básicamente, un procesador 8080 modificado con todas las líneas de datos conectadas a tierra mediante una resistencia de bajo valor, 100 ohm).

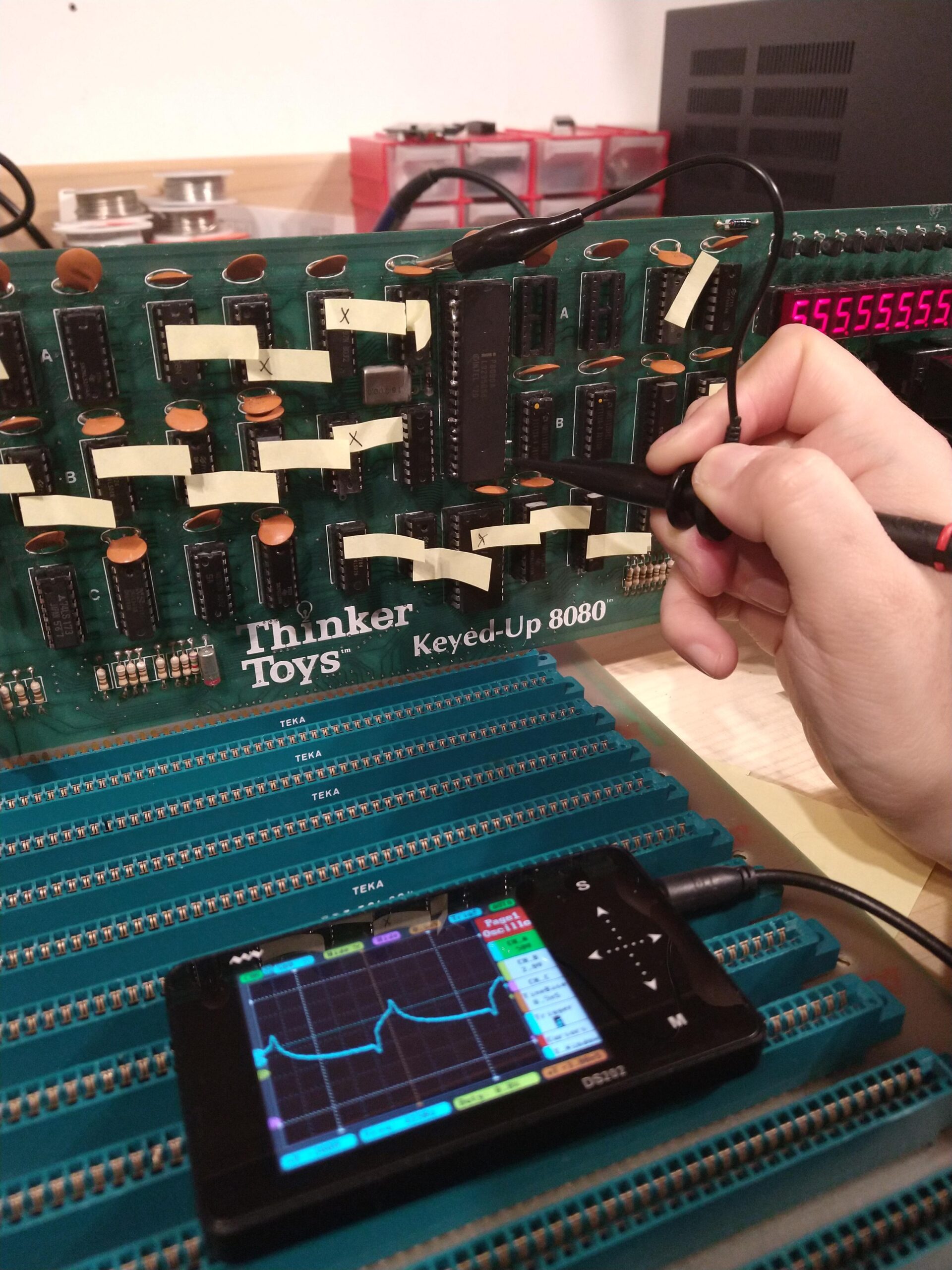

En una revisión más exhaustiva con el osciloscopio se observan el bus de direcciones caído, con una correcta señal de reloj en el pin de entrada del procesador, entre otras señales esenciales, pero observándose una señal de reset en estado HI (alto) de forma permanente.

Se realiza una revisión más en detalle del circuito que inicia el procesador. En base a la hoja de datos del mismo, se observa que el arranque requiere de un reset inicial para eliminar datos basura de diferentes registros internos y punteros del procesador.

Esto se realiza mediante el generador de reloj 8224 que suele acompañar al procesador 8080 en numerosas configuraciones, generando una señal en nivel alto (HI) en el pin de reset del procesador (acompañada de una señal READY) pero pasando a nive bajo (LO) dicha señal de reset al cabo de unos cuantos ciclos de reloj.

Desafortunadamente, y aparentemente debido a un fallo en el generador de reloj 8224, esto último no se estaba produciendo, por lo que el procesador se encontraba bloqueado con una señal de reset HI que no desaparecía y que no permitía continuar la secuencia de inicio.

A la espera de recibir un integrado de reemplazo, se realiza un puente temporal mediante un fragmento de cable que conecta a GND (pin 2 del procesador 8080) el pin de RESET (pin 12 del mismo integrado) una vez realizado el encendido, de tal forma que se desactiva la señal de reset y se continua con la secuencia de inicio.

Una vez obtenido el integrado de reemplazo se procede a sustitución observándose ya un funcionamiento correcto de la placa, y finalizando así la restauración de la misma.